在科技日新月異的今天,高精度的時間測量已經成為了各個領域不可或缺的一部分。其中,高精度子母鐘系統以其卓越的性能和穩定的輸出,成為了科研領域的首選。本文將深入探討高精度子母鐘系統的輸出理論,希望能為讀者提供一個全面而深入的理解。

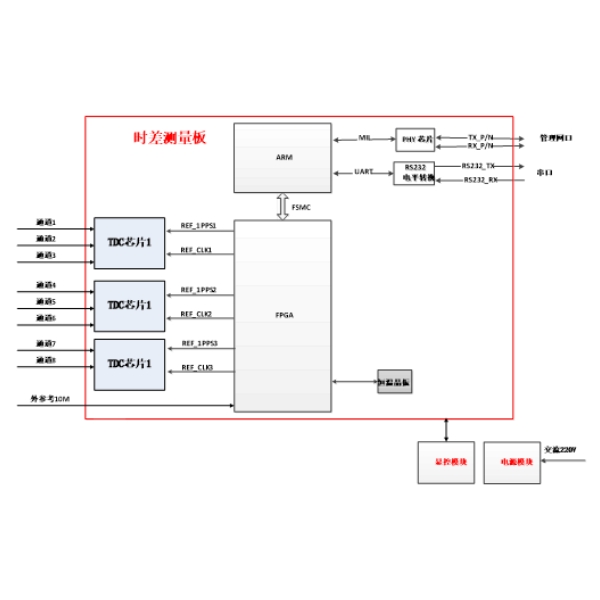

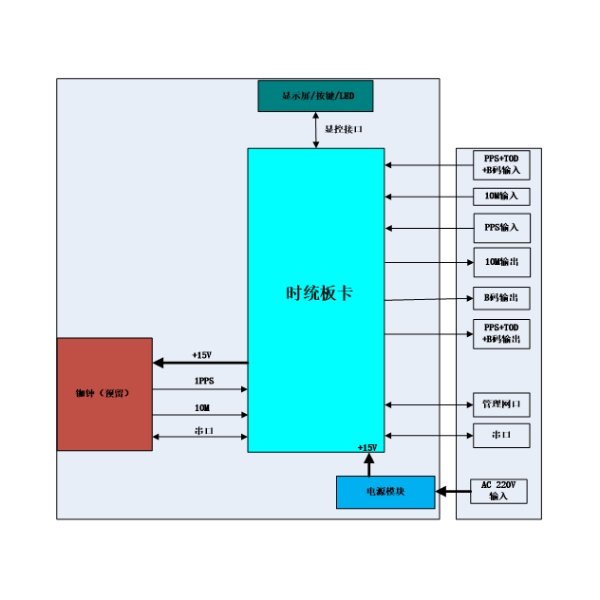

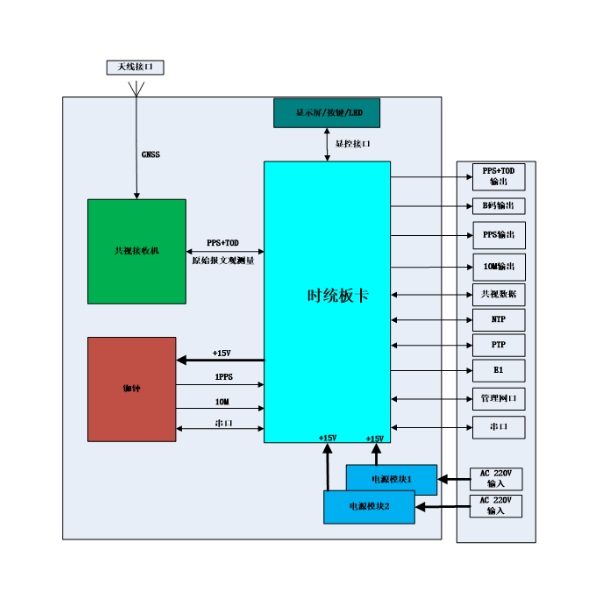

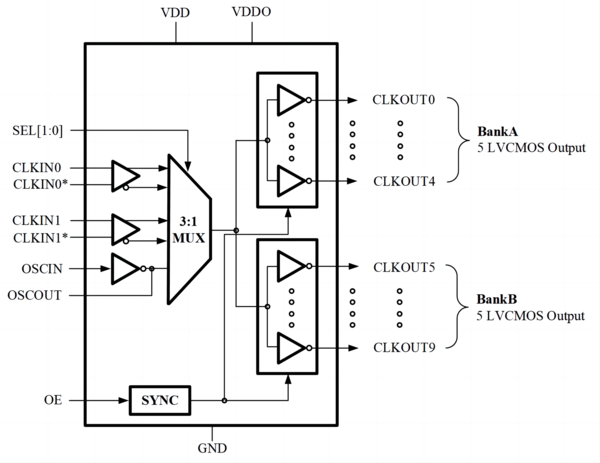

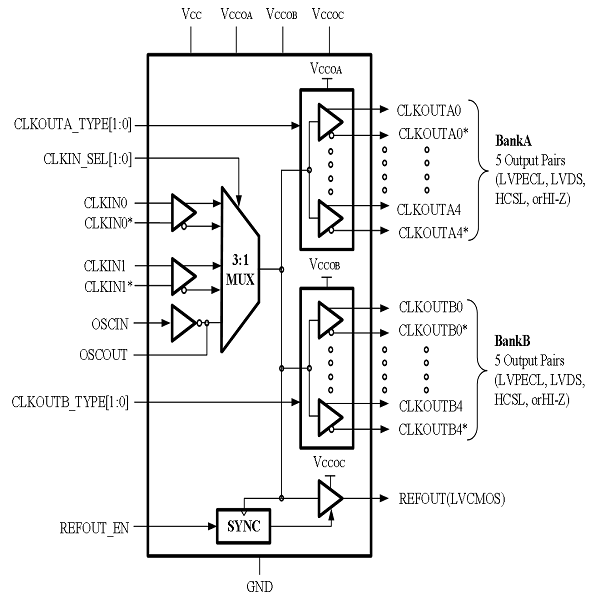

首先,我們需要明確什么是高精度子母鐘系統。子母鐘系統由一臺主時鐘和若干從時鐘組成,它們通過鎖相環路進行同步,從而實現精準的時間計量。主時鐘作為系統的“大腦”,負責產生并控制從時鐘的運行。從時鐘則按照主時鐘的頻率進行振蕩,輸出穩定、準確的時間信號。

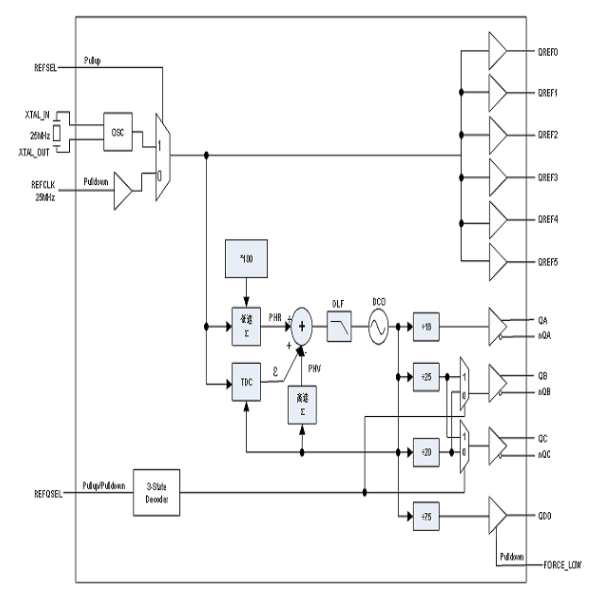

那么,高精度子母鐘系統的輸出理論是如何實現的呢?這主要依賴于鎖相環路(Phase-locked Loop,簡稱PLL)技術。PLL是一種反饋控制系統,通過比較輸入信號和期望信號之間的相位差,來調整電路的參數,使得系統的輸出與期望信號盡可能接近。在子母鐘系統中,PLL被用來調節從時鐘的頻率和相位,以保證其輸出的時間信號與主時鐘同步且誤差最小。

除了PLL技術,高精度子母鐘系統的輸出還受到其他因素的影響。例如,溫度的變化會影響電子元器件的工作狀態,從而影響系統的時間精度;電磁干擾也可能對系統的穩定性造成影響。因此,為了提高系統的穩定性和精度,需要對這些因素進行適當的處理和控制。

總的來說,高精度子母鐘系統的輸出理論是一個涉及到電子、光學、計算機等多個領域的復雜問題。通過對這個理論的研究和應用,我們可以更好地理解和控制高精度時間的產生和傳播,為科研、醫療、工業、交通等領域提供精準、可靠的時間服務。

時鐘系統

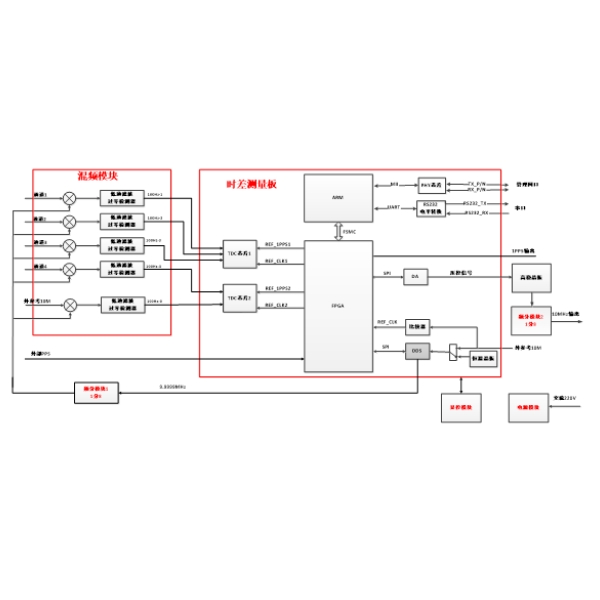

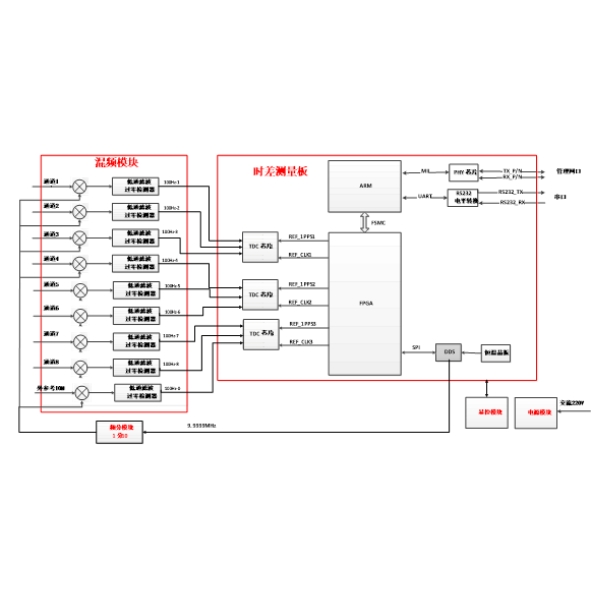

時鐘系統  芯片

芯片  晶振&原子鐘

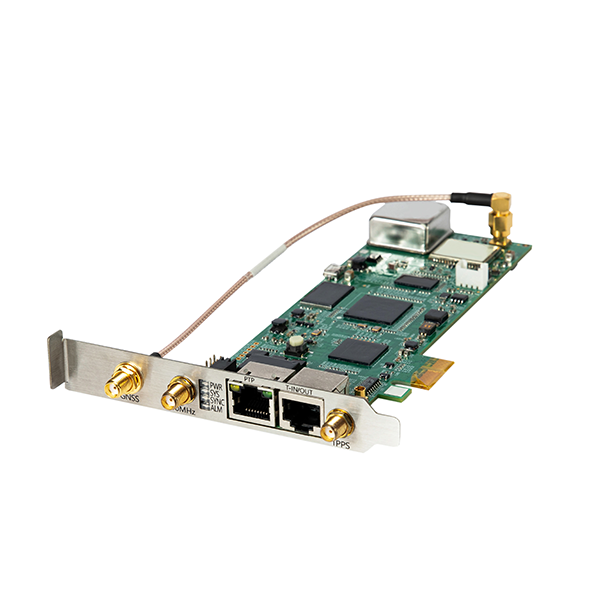

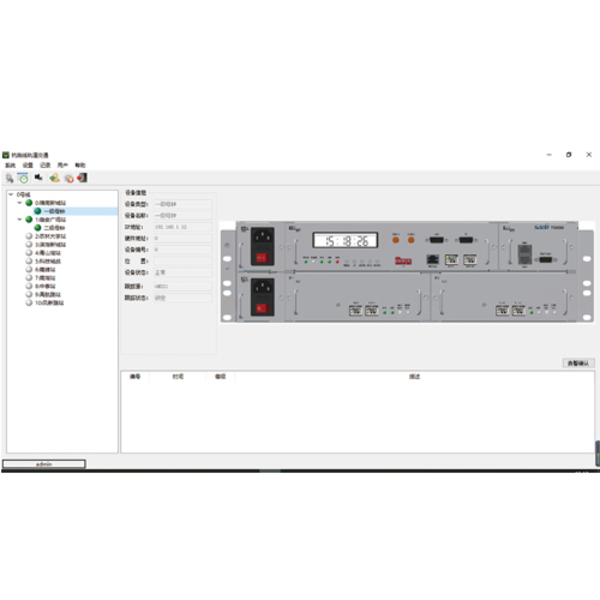

晶振&原子鐘  授時板卡 NTP時間同步服務器PTP時間同步服務器時間同步裝置授時安全防護裝置網同步設備/時頻一體化設備子母鐘系統BBU池時間同步時統設備鐘組設備測試儀器光纖雙向設備網管系統語音芯片時鐘發生器時鐘緩沖器時鐘SOC芯片超低噪聲OCXO超高穩OCXO小型化OCXO溫補晶振TCXO原子鐘時鐘模塊授時模塊

授時板卡 NTP時間同步服務器PTP時間同步服務器時間同步裝置授時安全防護裝置網同步設備/時頻一體化設備子母鐘系統BBU池時間同步時統設備鐘組設備測試儀器光纖雙向設備網管系統語音芯片時鐘發生器時鐘緩沖器時鐘SOC芯片超低噪聲OCXO超高穩OCXO小型化OCXO溫補晶振TCXO原子鐘時鐘模塊授時模塊

智能電網

智能電網

通信網絡

通信網絡

智慧交通

智慧交通

智能樓宇

智能樓宇

數據中心

數據中心

前沿領域

前沿領域

新聞資訊

新聞資訊

聯系我們

聯系我們

人才研學中心

人才研學中心

加入賽思

加入賽思

關于賽思

關于賽思